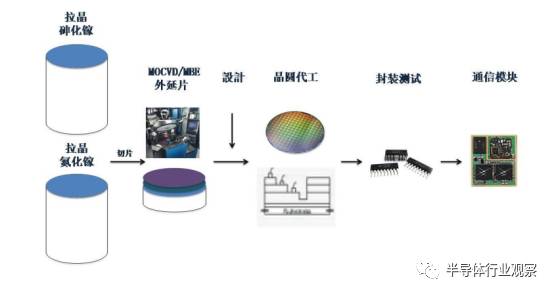

从硅片到软件 集成电路设计流程中的软件开发全景解析

集成电路(IC)设计是一个高度复杂、多阶段协同的系统工程,其成功不仅依赖于先进的半导体工艺和精密的物理设计,更离不开贯穿始终、不断演进的软件开发工作。现代IC设计流程本质上是“用软件设计硬件”的过程,软件开发已深度融入并驱动着每一个环节。

一、 前端设计:算法与架构的软件实现

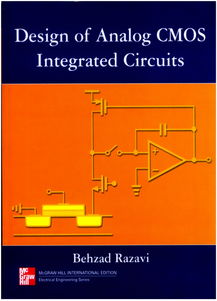

- 系统级建模与算法开发:设计始于概念。工程师使用高级建模语言(如SystemC、MATLAB/Simulink、Python)或专用电子系统级(ESL)工具,在软件环境中构建虚拟原型,进行系统架构探索、性能评估和算法验证。例如,为了一颗图像处理芯片,其核心的降噪、压缩算法首先会在软件层面实现和优化。

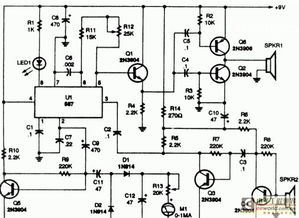

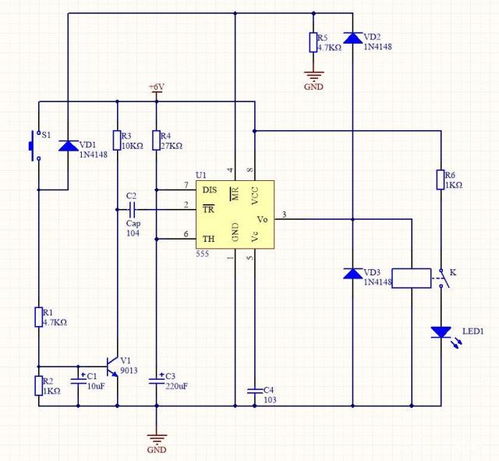

- 硬件描述语言(HDL)编码与仿真:这是核心的“设计输入”阶段。工程师使用Verilog或VHDL等HDL,以代码的形式描述数字电路的功能(行为级)或结构(RTL级)。利用仿真软件(如ModelSim、VCS、NC-Verilog)搭建测试平台(Testbench),通过运行大量的测试向量,在软件层面验证代码功能的正确性。这个过程高度依赖软件开发中的验证方法学,如受约束的随机测试、断言检查、功能覆盖率收集等。

- 逻辑综合与形式验证:RTL代码完成后,通过综合工具(如Design Compiler)将其转换为基于特定工艺库的门级网表。这个转换过程本身就是一个复杂的软件优化过程。之后,使用形式验证工具,从数学上严格证明综合后的网表与原始的RTL设计在功能上完全等价,替代了部分耗时的仿真。

二、 后端设计:物理实现的软件驱动

- 物理设计自动化:这是软件密集型领域。布局布线工具(如Innovus、ICC2)将门级网表转换成具体的物理版图。软件需要自动完成:

- 布局:决定数百万甚至数十亿个标准单元在芯片上的位置。

- 时钟树综合:构建低偏移、低功耗的全局时钟分布网络。

- 布线:在多层金属层上连接所有单元,满足时序、电学规则。

- 签核分析:进行静态时序分析、电源完整性分析、信号完整性分析等,确保设计满足性能、可靠性和功耗目标。所有这些工具的核心都是极其复杂的算法软件。

- 设计流程自动化与数据管理:面对海量的设计文件、工具脚本和版本,需要开发或集成强大的流程自动化框架和数据管理系统。这通常涉及Python、Tcl、Perl等脚本语言,用于串联工具、定制检查点、生成报告和实现自动化回归测试,显著提升设计效率和一致性。

三、 软硬协同与验证:软件开发的关键桥梁

- 固件与底层驱动开发:在芯片设计的与之配套的固件(Firmware)和硬件抽象层驱动开发就已启动。这些软件直接与芯片寄存器交互,是唤醒芯片、配置功能、实现基础控制的关键。它们通常在虚拟原型或FPGA原型平台上进行早期开发与验证。

- 原型验证与仿真加速:为了更早地运行真实的软件,会使用FPGA构建硬件仿真平台,或将设计映射到专用的仿真加速器(如Palladium, ZeBu)。此时,完整的操作系统或应用程序可以在“准芯片”上运行,进行软硬件联合调试,发现深层次交互问题。支持这些平台的软件工具链和调试环境开发至关重要。

四、 支撑环境:软件开发的基础设施

- 电子设计自动化工具开发:EDA(电子设计自动化)厂商(如Synopsys, Cadence, Siemens EDA)本身就是顶尖的软件公司。他们开发的综合、布局布线、仿真、验证工具,是IC设计流程的基石,集成了计算机科学、算法优化和芯片物理的最新成果。

- 工艺设计工具包开发:晶圆厂提供的PDK包含工艺文件、标准单元库、复杂IP的仿真模型等,其中大量的文件(如.lib, .lef, .gds)和配套的验证规则脚本,都是为EDA工具服务的“软件数据包”,其质量直接影响设计成败。

- 内部工具与脚本开发:大型芯片设计公司通常拥有庞大的内部软件开发团队,用于开发定制化工具、提升现有工具效率、构建统一的设计平台和数据分析系统,以形成独特的设计竞争力。

结论

集成电路设计流程与软件开发已密不可分。软件开发不仅是实现设计意图(前端编码)和实现物理转换(后端工具)的手段,更是进行架构探索、功能验证、性能分析和流程管理的核心驱动力。一颗先进芯片的诞生,是硬件架构师、电路设计师与软件算法工程师、工具开发工程师、验证工程师紧密协作的结晶。随着芯片规模扩大和系统复杂度提升,特别是面向人工智能、自动驾驶等领域的异构计算芯片兴起,基于软件的系统级设计、敏捷开发方法和持续集成/持续验证的理念,正变得比以往任何时候都更加重要。

如若转载,请注明出处:http://www.scchinaunicom-cdzf.com/product/55.html

更新时间:2026-04-14 19:17:03