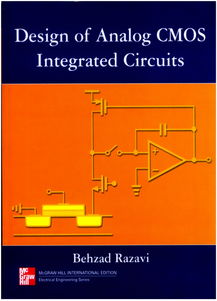

模拟集成电路设计精粹 第六章 集成电路设计全览

在《模拟集成电路设计精粹》的第六章中,作者深入探讨了现代集成电路设计的核心思想、设计流程与关键权衡。这一章不仅是理论知识的集大成者,也是连接抽象概念与物理实现的桥梁,为工程师提供了从架构规划到最终版图的全景式指引。

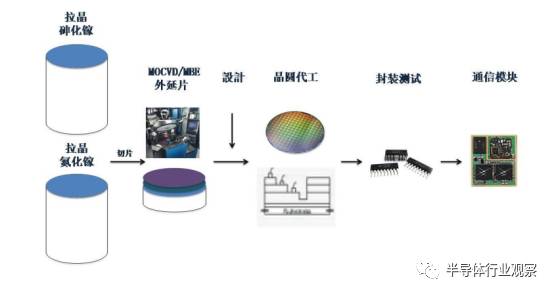

本章开宗明义地强调了集成电路设计的层次化思想。设计并非一蹴而就,而是从系统级规范(Specifications)开始,逐层分解为架构级、电路级、晶体管级乃至版图级的实现。这种自顶向下的方法(Top-Down Design)确保了设计的可控性与目标一致性,同时辅以自底向上的验证(Bottom-Up Verification),通过仿真和模型迭代修正,形成完整的设计闭环。层次化设计不仅管理了复杂性,也明晰了各阶段的设计目标与验证标准。

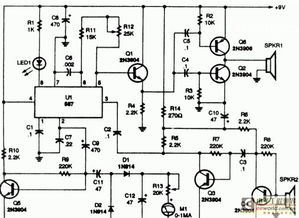

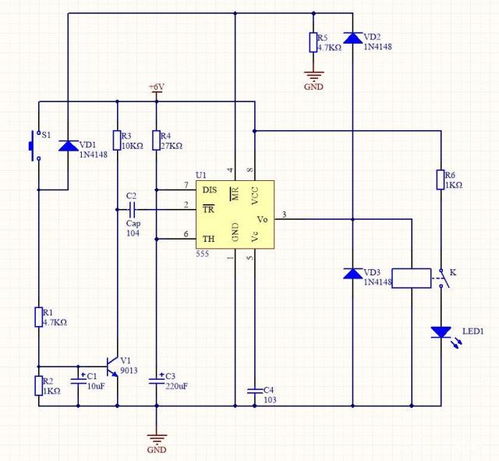

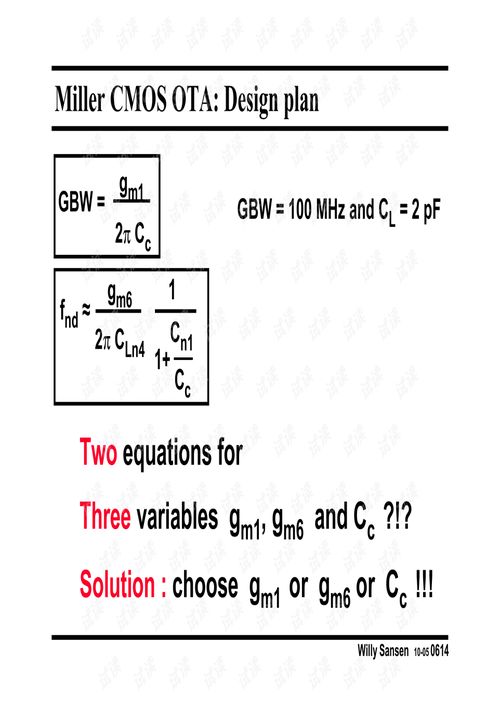

接着,文章聚焦于设计流程的核心环节:电路设计与仿真。在确定系统架构后,设计者需将功能模块转化为具体的晶体管级电路。这涉及到深入的器件物理知识,例如MOSFET的工作区域、增益、带宽、噪声与功耗特性。设计不再是孤立的参数计算,而是在多重约束下(如增益带宽积GBW、相位裕度、压摆率、电源电压抑制比PSRR)的优化过程。作者通过经典运放(如折叠共源共栅、两级运放)的设计实例,详细说明了如何通过手工分析与仿真工具(如SPICE)协同工作,逐步迭代以达到性能指标。这里,折衷(Trade-off)艺术展现得淋漓尽致:速度与精度、功耗与噪声、面积与成本之间的平衡,是模拟设计永恒的主题。

然后,本章过渡到版图设计(Layout Design)与物理实现。电路性能的最终保障,极大程度依赖于精心的版图规划。作者系统介绍了匹配性设计(如差分对、电流镜的共质心布局)、寄生效应控制(如减少寄生电容与电阻)、噪声隔离(如保护环、屏蔽层)以及可靠性考量(如天线效应、闩锁效应防护)。版图不仅是几何图形的绘制,更是电学特性的物理体现。设计规则检查(DRC)、电路图与版图一致性检查(LVS)以及后仿真(Post-layout Simulation)构成了确保制造正确性的三重关卡,任何疏忽都可能导致芯片失效或性能劣化。

本章以设计方法论收尾,指出了现代IC设计团队协作、IP复用以及设计自动化工具(如模拟电路综合、混合信号验证)的发展趋势。尽管工具日益强大,但设计者的洞察力与经验仍是不可替代的核心。第六章的精髓在于,它将集成电路设计描绘为一个兼具科学严谨性与工程创造性的过程:在数学方程与物理定律的框架内,通过巧妙的构思与细致的实现,将抽象创意转化为硅片上的高性能电路。

总而言之,第六章作为《模拟集成电路设计精粹》的关键部分,不仅提供了具体的设计技术与流程知识,更培养了读者系统化的设计思维。它提醒我们,优秀的模拟IC设计,是在深刻理解基本原理的基础上,于约束的海洋中精准航行的艺术,每一处细节都关乎最终芯片的灵魂——性能与可靠性。

如若转载,请注明出处:http://www.scchinaunicom-cdzf.com/product/53.html

更新时间:2026-04-15 20:34:29