大话集成电路71 EDA工具——芯片软件设计的利器

在当今这个信息爆炸的时代,芯片作为电子产品的“心脏”,其重要性不言而喻。从智能手机到超级计算机,从家用电器到航天器,几乎每一个现代设备都离不开芯片的驱动。你是否曾想过,这些集成了数十亿甚至数百亿个晶体管的复杂电路,是如何被设计出来的呢?答案就在于一套被称为“电子设计自动化”(EDA)的强大软件工具。

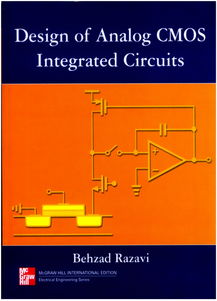

EDA工具,堪称集成电路设计领域的“瑞士军刀”。在芯片设计的每一个环节,从最初的构思到最终的制造,EDA工具都扮演着不可或缺的角色。我们可以将其比作建筑师手中的CAD软件,没有它,设计一座摩天大楼几乎是不可能完成的任务;同样,没有EDA工具,设计一颗先进的芯片也无异于天方夜谭。

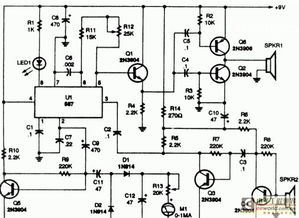

让我们从芯片设计的起点——逻辑设计说起。工程师们使用硬件描述语言(如Verilog或VHDL)来“描述”芯片需要实现的功能。这就像用一门特殊的编程语言来编写芯片的“行为规范”。EDA工具中的“逻辑综合”工具会将这种高级描述,转换成一连串的门级电路网表,即由基本逻辑门(如与门、或门、非门)构成的连接图。这个过程充满了优化,目标是在满足功能的前提下,追求更小的面积、更低的功耗和更快的速度。

接下来进入物理设计阶段,这是EDA工具大显身手的核心战场。想象一下,要把数亿个逻辑门和它们之间的连线,合理地“摆放”在一块指甲盖大小的硅片上,并确保所有信号能够正确、及时地传递,同时还要处理功耗、散热、制造工艺限制等一系列棘手问题。这其中的复杂程度,远超任何人类手工所能及。

- 布局规划:工具首先对芯片进行宏观规划,划分不同功能模块(如CPU核心、内存控制器等)的大致区域。

- 布局:将一个个具体的标准单元(实现基本逻辑功能的预制电路块)精确地放置在芯片版图上。

- 布线:在单元之间,根据逻辑连接关系,铺设数百万甚至数十亿条金属导线。这就像在一个极度拥挤的城市里规划所有道路,且不能有任何短路或断路。现代EDA的布线算法极其智能,能自动绕开障碍,优化路径。

- 时序分析与优化:确保信号从一点传到另一点的时间满足设计要求。芯片时钟频率高达数GHz,任何微小的延迟差错都可能导致功能失败。工具会反复迭代,调整布局布线,直至满足所有时序约束。

- 物理验证:在交付制造前,进行一系列严格的“体检”,检查版图是否符合制造工艺的设计规则(DRC),电路连接是否与原始设计一致(LVS),以及是否存在信号完整性、电迁移等可靠性问题。

除了这些核心步骤,EDA工具还覆盖了模拟电路设计、芯片封装设计、功耗分析、可测试性设计等方方面面。随着工艺进入纳米乃至更先进的节点,设计复杂度呈指数级增长,EDA工具也日益集成人工智能和机器学习技术,以帮助工程师应对“设计围墙”的挑战。

可以说,EDA是连接芯片创意与硅片实物的桥梁。没有这套强大的软件利器,我们手中那些功能强大的芯片将永远停留在图纸阶段。它不仅是设计工具,更是创新加速器,持续推动着集成电路产业向着更高性能、更低功耗、更小尺寸的方向迈进。因此,当我们为新一代芯片的突破而欢呼时,也请不要忘记背后那些默默无闻的EDA工具及其开发者们,他们正是芯片软件设计王国里真正的“铸剑大师”。

如若转载,请注明出处:http://www.scchinaunicom-cdzf.com/product/50.html

更新时间:2026-04-18 04:21:13